Produktuak Kategoria

- FM transmisorea

- 0-50w 50w-1000w 2kw-10kw 10kw +

- TV igorlea

- 0-50w 50-1kw 2kw-10kw

- FM antena

- telebista antena

- Antena Osagarriak

- Kable Connector Power Splitter Karga Dummy

- RF Transistor

- Energia hornidura

- Audio Ekipamenduak

- DTV Front End Ekipamendua

- Link System

- STL sistema Mikrouhin Link sistema

- FM irratia

- Power Meter

- Beste produktu batzuk

- Berezia Coronaviruserako

Produktuak Tags

fmuser Sites

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> afrikaansa

- sq.fmuser.net -> Albaniera

- ar.fmuser.net -> arabiera

- hy.fmuser.net -> Armenian

- az.fmuser.net -> azerbaijanera

- eu.fmuser.net -> euskara

- be.fmuser.net -> Bielorrusiera

- bg.fmuser.net -> Bulgarian

- ca.fmuser.net -> Katalana

- zh-CN.fmuser.net -> Txinera (sinplifikatua)

- zh-TW.fmuser.net -> Chinese (Traditional)

- hr.fmuser.net -> kroaziera

- cs.fmuser.net -> Txekiera

- da.fmuser.net -> Danimarkarra

- nl.fmuser.net -> Holandako

- et.fmuser.net -> Estoniera

- tl.fmuser.net -> Filipinoa

- fi.fmuser.net -> finlandiera

- fr.fmuser.net -> Frantsesa

- gl.fmuser.net -> Galiziera

- ka.fmuser.net -> Georgiarra

- de.fmuser.net -> alemana

- el.fmuser.net -> Greek

- ht.fmuser.net -> Haitiko kreolera

- iw.fmuser.net -> Hebreera

- hi.fmuser.net -> Hindi

- hu.fmuser.net -> Hungarian

- is.fmuser.net -> Islandiera

- id.fmuser.net -> Indonesiera

- ga.fmuser.net -> Irlandera

- it.fmuser.net -> Italian

- ja.fmuser.net -> Japoniera

- ko.fmuser.net -> Koreera

- lv.fmuser.net -> Letoniera

- lt.fmuser.net -> Lithuanian

- mk.fmuser.net -> mazedoniera

- ms.fmuser.net -> malaysiera

- mt.fmuser.net -> maltera

- no.fmuser.net -> Norwegian

- fa.fmuser.net -> persiera

- pl.fmuser.net -> poloniera

- pt.fmuser.net -> Portugesa

- ro.fmuser.net -> Romanian

- ru.fmuser.net -> errusiera

- sr.fmuser.net -> serbiera

- sk.fmuser.net -> Eslovakiera

- sl.fmuser.net -> Slovenian

- es.fmuser.net -> Gaztelania

- sw.fmuser.net -> Swahilia

- sv.fmuser.net -> Suediera

- th.fmuser.net -> Thai

- tr.fmuser.net -> Turkiera

- uk.fmuser.net -> ukrainera

- ur.fmuser.net -> urdua

- vi.fmuser.net -> Vietnamese

- cy.fmuser.net -> galesera

- yi.fmuser.net -> Yiddish

PMOS eta NMOS transistoreak

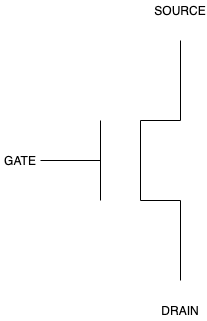

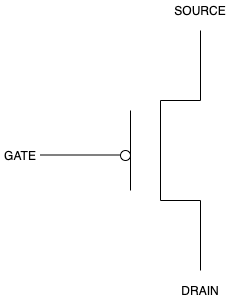

Mikroprozesadoreak transistorez eraikita daude. Bereziki, MOS transistoreez eraikita daude. MOS Metal-Oxide Semiconductor akronimoa da. Bi MOS transistore mota daude: pMOS (positibo-MOS) eta nMOS (negatibo-MOS). pMOS eta nMOS bakoitzak hiru osagai nagusi ditu: atea, iturria eta hustubidea.

pMOS eta nMOS batek nola funtzionatzen duten behar bezala ulertzeko, garrantzitsua da lehenik eta behin termino batzuk definitzea:

zirkuitu itxia: horrek esan nahi du elektrizitatea atetik iturrira doala.

zirkuitu irekia: horrek esan nahi du elektrizitatea ez dela atetik iturrira isurtzen; baizik eta elektrizitatea atetik hustubidera doa.

NMOS transistore batek arbuiagarria ez den tentsioa jasotzen duenean, iturritik hustubiderako konexioak hari gisa jokatzen du. Elektrizitatea iturritik hustubidera eragotzi gabe joango da - zirkuitu itxia deritzo. Bestalde, nMOS transistore batek 0 volt inguruko tentsioa jasotzen duenean, iturritik drainera arteko konexioa hautsi egingo da eta zirkuitu irekia deritzo.

p motako transistoreak n motako transistorearen aurka funtzionatzen du. nMOS-ek iturburuarekin zirkuitu itxia osatuko du tentsioa baztergarria ez denean, pMOSek zirkuitu irekia osatuko du iturriarekin tentsioa ez da baztergarria denean.

Goian erakusten den pMOS transistorearen irudian ikus dezakezun bezala, pMOS transistorearen eta nMOS transistorearen arteko desberdintasun bakarra atearen eta lehen barraren arteko zirkulu txikia da. Zirkulu honek tentsioaren balioa alderantzikatzen du; beraz, ateak 1 balio baten tentsio adierazgarria bidaltzen badu, inbertsoreak 1a 0ra aldatuko du eta zirkuitua horren arabera funtzionatzea eragingo du.

pMOS eta nMOS modu kontrako batean funtzionatzen dutenez, modu osagarrian, biak MOS zirkuitu erraldoi batean konbinatzen ditugunean, cMOS zirkuitu deritzo, metal-oxido erdieroale osagarria deritzona.

MOS zirkuituak erabiltzea

pMOS eta nMOS zirkuituak konbina ditzakegu GATES izeneko egitura konplexuagoak eraikitzeko, zehatzago: ate logikoak. Funtzio logiko hauen kontzeptua eta haiei lotutako egia-taulen kontzeptua sartu dugu aurreko blogean, klik eginez aurki dezakezuna. hemen.

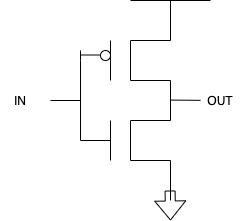

Iturrira konektatzen den pMOS transistore bat eta lurrera konektatzen den nMOS transistore bat erantsi ditzakegu. Hau cMOS transistore baten lehen adibidea izango da.

CMOS transistore honek NOT funtzio logikoaren antzera jokatzen du.

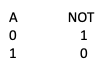

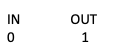

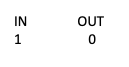

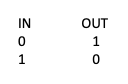

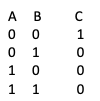

Ikus diezaiogun NOT egia taulari:

NOT egia taulan, sarrerako balio bakoitza: A alderantzikatu egiten da. Zer gertatzen da goiko zirkuituarekin?

Beno, pentsa dezagun sarrera 0 bat dela.

0-a sartzen da eta haritik gora eta behera doa bai pMOSera (goian) bai nMOSra (behean). 0 balioa pMOSera iristen denean, 1era alderantzikatzen da; beraz, iturriarekiko konexioa itxita dago. Honek 1 balio logikoa sortuko du lurrarekiko (hustubidea) konexioa ere itxita ez dagoen bitartean. Tira, transistoreak osagarriak direnez, badakigu nMOS transistoreak ez duela balioa alderantzikatuko; beraz, 0 balioa dagoen bezala hartzen du eta —beraz— zirkuitu ireki bat sortuko du lurrera (draina). Horrela, 1 balio logikoa sortzen da atearentzat.

Zer gertatzen da 1 bat IN balioa bada? Beno, aurreko urrats berdinak jarraituz, 1 balioa pMOS-era eta nMOS-era bidaltzen da. pMOS-ek balioa jasotzen duenean, balioa 0-ra alderantzikatzen da; horrela, ITURRIrako konexioa irekita dago. NMOS-ek balioa jasotzen duenean, balioa ez da alderantzikatzen; horrela, balioak 1 izaten jarraitzen du. nMOSek 1 balio bat jasotzen duenean, konexioa itxi egiten da; beraz, lurrarekiko konexioa itxita dago. Honek 0 balio logikoa sortuko du.

Sarrera/irteera bi multzoak bateratzeak etekinak ematen ditu:

Nahiko erraza da egia-taula hau funtzio logikoak EZ sortzen duenaren berdina dela ikustea. Beraz, hau NOT atea bezala ezagutzen da.

Erabili al ditzakegu bi transistore sinple hauek egitura konplikatuagoak egiteko? Erabat! Jarraian, NOR atea eta OR atea eraikiko ditugu.

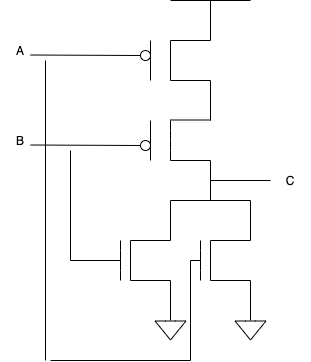

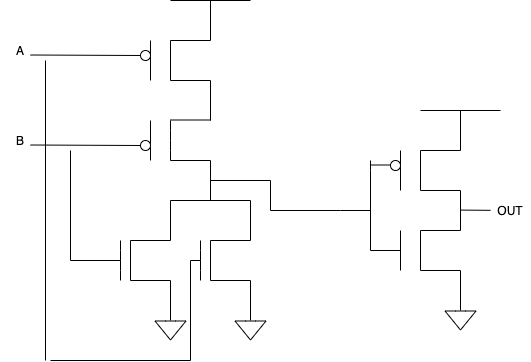

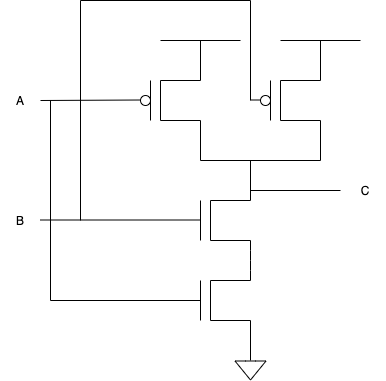

Zirkuitu honek bi pMOS transistore erabiltzen ditu goiko aldean eta bi nMOS transistore behealdean. Berriz ere, ikus dezagun atearen sarrera nola jokatzen duen ikusteko.

A 0 denean eta B 0 denean, ate honek bi balioak 1era alderantzikatuko ditu pMOS transistoreetara iristen direnean; hala ere, nMOS transistoreek 0-ko balioa mantenduko dute. Horrek ateak 1-eko balioa ekoitziko du.

A 0 denean eta B 1 denean, ate honek bi balioak alderantzikatuko ditu pMOS transistoreetara iristen direnean; beraz, A 1era aldatuko da eta B 0. Horrek ez du iturrira eramango; bi transistoreek zirkuitu itxia behar baitute sarrera iturrira konektatzeko. nMOS transistoreek ez dituzte balioak alderantzikatzen; beraz, A-ri lotutako nMOSek 0 bat sortuko du, eta B-ri lotutako nMOSek 1 bat; horrela, B-ri lotutako nMOSak zirkuitu itxia sortuko du lurrera. Honek ateak 0 balio bat sortzera eramango du.

A 1 denean eta B 0 denean, ate honek bi balioak alderantzikatuko ditu pMOS transistoreetara iristen direnean; beraz, A 0-ra aldatuko da eta B 1-era aldatuko da. Horrek ez du iturrira eramango; bi transistoreek zirkuitu itxia behar baitute sarrera iturrira konektatzeko. nMOS transistoreek ez dituzte balioak alderantzikatzen; beraz, A-ri lotutako nMOSek 1 bat sortuko du, eta B-ri lotutako nMOSek 0 bat; horrela, A-rekin lotutako nMOSek zirkuitu itxi bat sortuko du lurrera. Honek ateak 0 balio bat sortzera eramango du.

A 1 denean eta B 1 denean, ate honek bi balioak alderantzikatuko ditu pMOS transistoreetara iristen direnean; beraz, A 0-ra aldatuko da eta B 0-ra aldatuko da. Horrek ez du iturrira eramango; bi transistoreek zirkuitu itxia behar baitute sarrera iturrira konektatzeko. nMOS transistoreek ez dituzte balioak alderantzikatzen; beraz, A-ri lotutako nMOSek 1 bat sortuko du, eta B-ri lotutako nMOSek 1 bat; horrela, A-ri lotutako nMOSek eta B-ri lotutako nMOSek zirkuitu itxia sortuko dute lurrera. Honek ateak 0 balio bat sortzera eramango du.

Beraz, atearen egia-taula hau da:

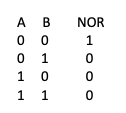

Bien bitartean, NOR funtzio logikoaren egia-taula hau da:

Horrela, ate hau NOR ate bat dela baieztatu dugu, bere egia-taula NOR funtzio logikoarekin partekatzen duelako.

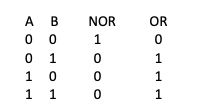

Orain, orain arte sortu ditugun bi ateak elkarrekin jarriko ditugu EDO ate bat sortzeko. Gogoratu, NOR NOT OR esan nahi du; beraz, jada alderantzikatuta dagoen ate bat alderantzikatzen badugu, jatorrizkoa berreskuratuko dugu. Proba dezagun hau martxan ikusteko.

Hemen egin duguna da aurretik NOR atea hartu dugula eta irteeran NOT atea aplikatu dugula. Goian erakutsi dugun bezala, NOT ateak 1 balioa hartuko du eta 0 bat aterako du, eta NOT ateak 0 balioa hartuko du eta 1 bat aterako du.

Honek NOR atearen balioak hartuko ditu eta 0 guztiak 1 eta 1ak 0 bihurtuko ditu. Horrela, egia-taula hau izango da:

Ate hauek probatzen gehiago praktikatu nahi baduzu, lasai probatu goiko balioak zuk zeuk eta ikusi ateak emaitza baliokideak sortzen dituela!

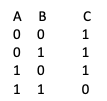

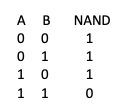

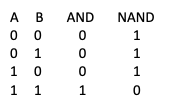

Hau NAND ate bat dela aldarrikatzen dut, baina proba dezagun ate honen egia-taula benetan NAND atea den zehazteko.

A 0 denean eta B 0 denean, Aren pMOSek 1 bat sortuko du, eta Aren nMOSek 0 bat; horrela, ate honek 1 logikoa sortuko du, iturriari zirkuitu itxi batekin konektatua eta zirkuitu ireki batekin lurretik deskonektatuta dagoelako.

A 0 denean eta B 1 denean, Aren pMOSek 1 bat sortuko du, eta Aren nMOSek 0 bat; horrela, ate honek 1 logikoa sortuko du, iturriari zirkuitu itxi batekin konektatua eta zirkuitu ireki batekin lurretik deskonektatuta dagoelako.

A 1 denean eta B 0 denean, B-ren pMOSek 1 bat sortuko du, eta B-ren nMOSek 0 bat; horrela, ate honek 1 logikoa sortuko du, iturriari zirkuitu itxi batekin konektatua eta zirkuitu ireki batekin lurretik deskonektatuta dagoelako.

A 1 denean eta B 1 denean, A-ren pMOSek 0 bat sortuko du, eta A-ren nMOSek 1 bat; beraz, B-ren pMOS eta nMOS egiaztatu behar ditugu, gainera. B-ren pMOSek 0 bat sortuko du, eta B-ren nMOSek 1 bat; horrela, ate honek 0 logiko bat sortuko du, iturritik zirkuitu ireki batekin deskonektatuta eta zirkuitu itxi batekin lurretik konektatzen baita.

Egia-taula hau da:

Bien bitartean, NAND funtzio logikoaren egia-taula hau da:

Hori dela eta, egiaztatu dugu NAND ate bat dela.

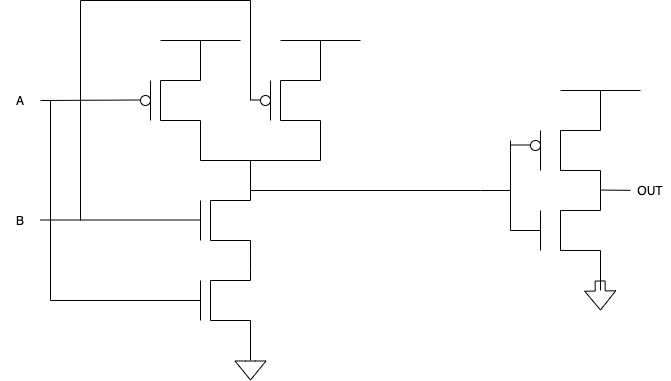

Orain, nola eraikiko dugu ETA atea? Beno, ETA atea eraikiko dugu NOR ate batetik EDO atea eraiki genuen modu berean! Inbertsore bat erantsiko dugu!

Egin dugun guztia NAND ate baten irteeran NOT funtzio bat aplikatzen denez, egia-taulak honela izango du:

Berriz ere, mesedez egiaztatu, esaten dizudana egia dela ziurtatzeko.

Gaur egun, pMOS eta nMOS transistoreak zer diren azaldu dugu, baita nola erabili egitura konplexuagoak eraikitzeko! Espero dut blog hau informatzailea aurkitzea. Nire aurreko blogak irakurri nahi badituzu, behean aurkituko duzu zerrenda.